Beli Stasiun Pengerjaan Ulang BGA

1. Anda dapat membeli BGA Rework Station langsung dari produsen aslinya.2. Stasiun Pengerjaan Ulang BGA Otomatis DH-A2.3. Mikrometer untuk penyesuaian sudut BGA dan penyesuaian motherboard.4. Pelabuhan: Shenzhen.

Deskripsi

Beli Stasiun Pengerjaan Ulang BGA

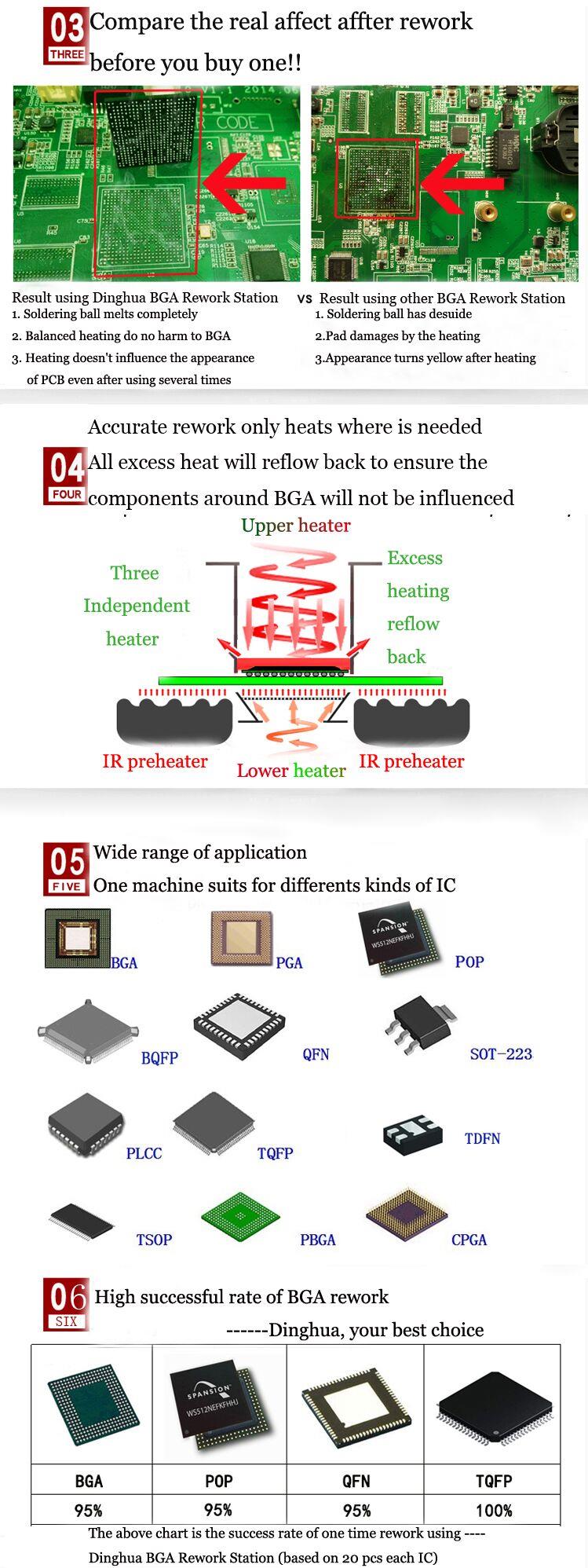

1.Aplikasi Stasiun Pengerjaan Ulang BGA Optik Otomatis

Bekerja dengan semua jenis motherboard atau PCBA.

Solder, reball, pematrian berbagai jenis chip: BGA,PGA,POP,BQFP,QFN,SOT223,PLCC,TQFP,TDFN,TSOP,

PBGA, CPGA, chip LED.

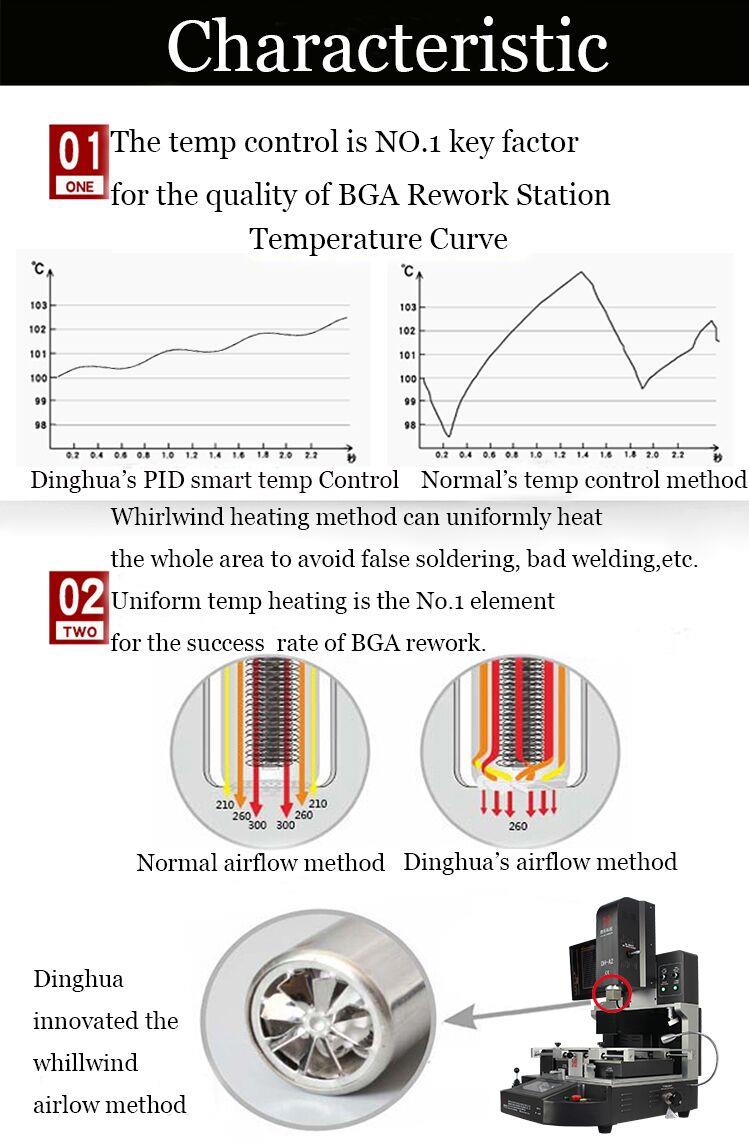

2. Fitur Produk dariOptik OtomatisStasiun Pengerjaan Ulang BGA

3.SpesifikasiOptik OtomatisStasiun Pengerjaan Ulang BGA

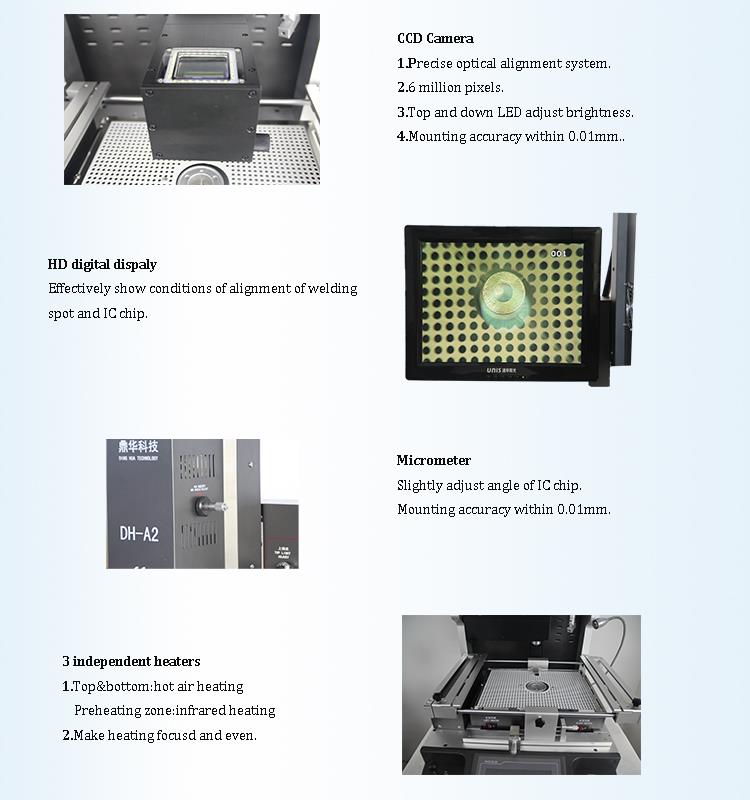

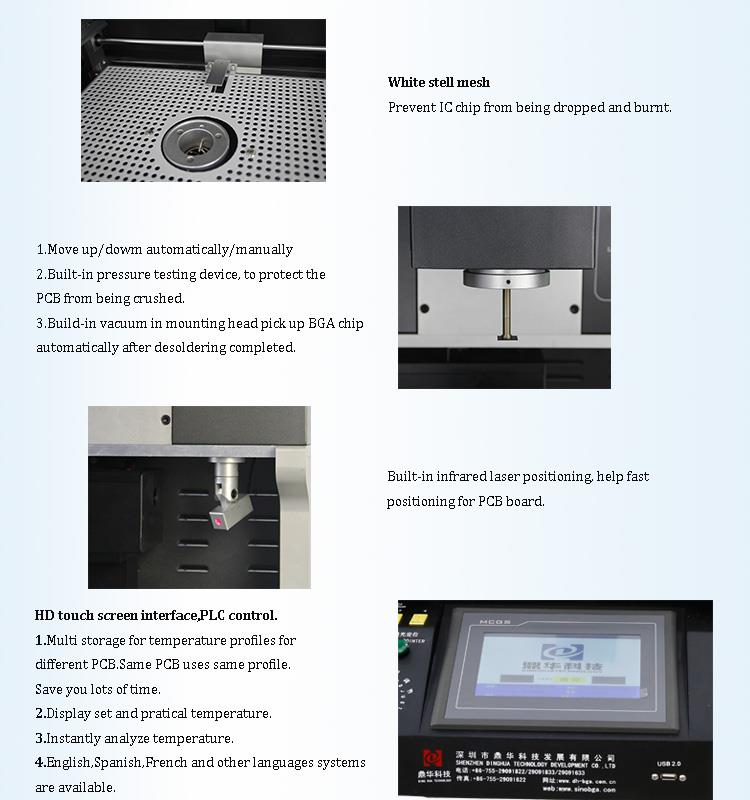

4.Detail dariOptik OtomatisStasiun Pengerjaan Ulang BGA

5. Mengapa Memilih KamiOptik OtomatisStasiun Pengerjaan Ulang BGA?

6.SertifikatOptik OtomatisStasiun Pengerjaan Ulang BGA

Sertifikat UL, E-MARK, CCC, FCC, CE ROHS. Sedangkan untuk meningkatkan dan menyempurnakan sistem mutu,

Dinghua telah lulus sertifikasi audit di tempat ISO, GMP, FCCA, C-TPAT.

7. Pengepakan & PengirimanOtomatisStasiun Pengerjaan Ulang BGA

8. Pengiriman untukOptik OtomatisMesin BGA Reballing

DHL/TNT/FEDEX. Jika Anda ingin istilah pengiriman lainnya, silakan beritahu kami. Kami akan mendukung Anda.

9. Ketentuan Pembayaran

Transfer bank, Western Union, Kartu Kredit.

Silakan beritahu kami jika Anda memerlukan dukungan lainnya.

10. Bagaimana cara kerja Mesin Reballing IC BGA Otomatis DH-A2?

11. Pengetahuan terkait

Tentang chip flash

Dinamika pasokan

Baru-baru ini, perusahaan chip pemilik baru SandForce, LSI, mengatakan bahwa mereka sedang mengembangkan firmware baru untuk SSD master SF

di Ultrabook. Fungsi utamanya adalah untuk mengurangi konsumsi daya SSD, dan juga meningkatkan kinerjanya

SSD dan percepat startup. kecepatan.

parameter

3. Catu daya 3V;

Array sel memori internal chip adalah (256M + 8.192M) bit × 8bit, dan register data serta memori buffer keduanya

(2k + 64) sedikit × 8bit;

Port I/O dengan multiplexing instruksi/alamat/data;

Perintah program dan penghapusan dapat ditangguhkan selama konversi daya;

Berkat teknologi gerbang bergerak CMOS yang andal, chip ini dapat mencapai siklus program/penghapusan maksimum 100kB, yang

menjamin penyimpanan data selama 10 tahun tanpa kehilangan.

Status kerja

I/O0~I/O7: port input dan output data, port I/O sering digunakan untuk input instruksi dan alamat serta input/output data,

dimana data berada

Masuk selama proses membaca. Ketika chip tidak dipilih atau tidak dapat dikeluarkan, port I/O berada dalam keadaan impedansi tinggi.

CLE: Latch instruksi digunakan untuk mengaktifkan instruksi ke jalur register instruksi dan mengunci instruksi pada

peningkatan WE dan CLE tinggi.

ALE: Address latch, digunakan untuk mengaktifkan jalur alamat ke register alamat internal, dan alamat tersebut di-latch pada

kenaikan WE dan ALE tinggi.

CE: Pemilih Chip, digunakan untuk mengontrol pemilihan perangkat. Saat perangkat sibuk, CE tinggi dan diabaikan, dan perangkat tidak dapat kembali

ke keadaan siaga.

RE: Baca aktifkan, digunakan untuk mengontrol keluaran data berkelanjutan dan mengirim data ke bus I/O. Data keluaran hanya valid pada

tepi jatuh RE, dan juga dapat mengakumulasi alamat data internal.

WE: Terminal aktifkan tulis digunakan untuk mengontrol penulisan instruksi pada port I/O. Pada saat yang sama, perintah, alamat

dan data dapat dilekatkan pada ujung pulsa WE yang meningkat melalui port ini.

WP: Pelindung penulisan, yang dapat dilindungi penulisan dalam konversi daya melalui terminal WP. Ketika WP rendah, itu internal

generator tingkat tinggi akan diatur ulang.

R/ B : Keluaran Siap/Sibuk, keluaran R/B dapat menunjukkan status pengoperasian perangkat. Ketika R/B rendah, hal ini menunjukkan bahwa suatu program,

operasi penghapusan atau pembacaan acak sedang berlangsung. Setelah operasi selesai, R/B secara otomatis akan kembali ke level tinggi. Sejak itu

terminal adalah keluaran saluran terbuka, ia tidak akan berada dalam keadaan impedansi tinggi bahkan ketika chip tidak dipilih atau keluaran dinonaktifkan.

PRE: Operasi baca penyalaan, digunakan untuk mengontrol operasi baca otomatis saat daya menyala, dan terminal PRE dapat dihubungkan

Ke VCC untuk mewujudkan operasi pembacaan otomatis penyalaan.

VCC: Terminal daya chip.

VSS: Tanah chip.

NC: Menggantung.

Pengeditan status pekerjaan

Operasi baca 1 halaman

Status default chip flash adalah status baca. Operasi baca adalah memulai instruksi dengan menulis alamat 00h ke

register instruksi melalui 4 siklus alamat. Setelah instruksi dikunci, operasi baca tidak dapat ditulis di halaman berikutnya.

Data dapat dikeluarkan secara acak dari satu halaman dengan menulis instruksi keluaran data acak. Alamat data dapat ditemukan secara otomatis

alamat berikutnya dengan instruksi keluaran acak dari alamat data yang akan dikeluarkan. Operasi keluaran data acak dapat digunakan berkali-kali

waktu.

Pemrograman 2 halaman

Pemrograman chip flash adalah halaman demi halaman, tetapi mendukung beberapa pemrograman halaman parsial dalam satu siklus pemrograman halaman,

sedangkan jumlah halaman berturut-turut dari sebagian halaman adalah 2112. Pengoperasian program dapat dimulai dengan menulis ke halaman program

instruksi pengakuan (10 jam), tetapi data kontinu harus dimasukkan sebelum instruksi (10 jam) ditulis.

Memuat data secara terus menerus Setelah menulis instruksi input data berkelanjutan (80 jam), ini akan memulai 4 siklus input alamat dan pemuatan data, tetapi

kata tersebut berbeda dengan data yang diprogram, tidak perlu dimuat. Chip ini mendukung input data acak di halaman dan dapat

secara otomatis mengubah alamat sesuai dengan perintah input data acak (85 jam). Entri data acak juga dapat digunakan beberapa kali.

3 pemrograman cache

Pemrograman cache adalah jenis pemrograman halaman yang dapat dilakukan oleh register data 2112-byte dan hanya valid dalam satu blok. Karena

chip flash memiliki buffer halaman, ia dapat melakukan input data terus menerus ketika register data diprogram ke dalam sel memori. Cache

pemrograman hanya dapat dimulai setelah akhir siklus pemrograman yang tidak lengkap dan register data dilewatkan dari cache. Pemrograman internal dapat dinilai dari pin R/B. Jika sistem hanya menggunakan R/B untuk memantau kemajuan program, maka urutan halaman terakhir

program target harus diatur oleh instruksi pemrograman halaman saat ini.

4 unit penyimpanan sulih suara

Efek ini dapat dengan cepat dan efisien menimpa data dalam suatu halaman tanpa mengakses memori eksternal. Sejak waktu yang dihabiskan terus menerus

akses dan pemuatan ulang dipersingkat, kemampuan eksekusi sistem ditingkatkan. Terutama ketika bagian dari blok ditingkatkan dan

sisa blok perlu disalin ke blok baru, kelebihannya ditunjukkan dengan jelas. Operasi ini adalah perintah baca yang dijalankan secara terus menerus,

tetapi tidak memerlukan akses terus menerus dan penyalinan program dari alamat tujuan. Operasi baca alamat halaman asli

instruksi "35h" dapat mentransfer seluruh 2112 byte data ke buffer data internal. Ketika chip kembali ke keadaan siap, halaman akan disalin

instruksi input data dengan loop alamat tujuan ditulis. Program kesalahan dalam operasi ini diberikan dengan status "lulus/gagal". Namun,

jika operasi memakan waktu terlalu lama untuk dijalankan, kesalahan operasi bit akan terjadi karena kehilangan data, mengakibatkan kesalahan eksternal "periksa/perbaiki" pemeriksaan perangkat

kegagalan. Oleh karena itu, operasi tersebut harus diperbaiki dengan dua kesalahan.

5 blok dihapus

Operasi penghapusan chip flash dilakukan berdasarkan blok. Pemuatan alamat blok akan dimulai dengan instruksi penghapusan blok dan diselesaikan dalam dua siklus. Faktanya, ketika baris alamat A12 hingga A17 dibiarkan mengambang, hanya baris alamat A18 hingga A28 yang tersedia. Penghapusan dapat dimulai dengan memuat perintah konfirmasi penghapusan dan alamat blok. Operasi ini harus dilakukan untuk mencegah isi memori terpengaruh oleh gangguan eksternal dan menyebabkan kesalahan penghapusan.

6 status dibaca

Daftar status dalam chip flash mengonfirmasi bahwa program dan operasi penghapusan berhasil diselesaikan. Setelah instruksi tulis (70 jam) ke register instruksi, siklus baca mengeluarkan isi register status ke I/O di tepi jatuh CE atau RE. Register instruksi akan tetap dalam keadaan baca sampai instruksi baru tiba, jadi jika register status dalam keadaan membaca selama siklus baca acak, maka instruksi baca harus diberikan sebelum siklus baca dimulai.