Stasiun Ulang BGA Optik Otomatis

Banyak digunakan dalam perbaikan tingkat chip untuk motherboard ponsel, laptop, komputer, TV, AC dll. Ini memiliki tingkat keberhasilan perbaikan yang tinggi dan otomatisasi tingkat tinggi dan menghemat banyak upaya manusia. Kami adalah produsen profesional mesin ini dan menyediakan mesin ini dalam stok.

Deskripsi

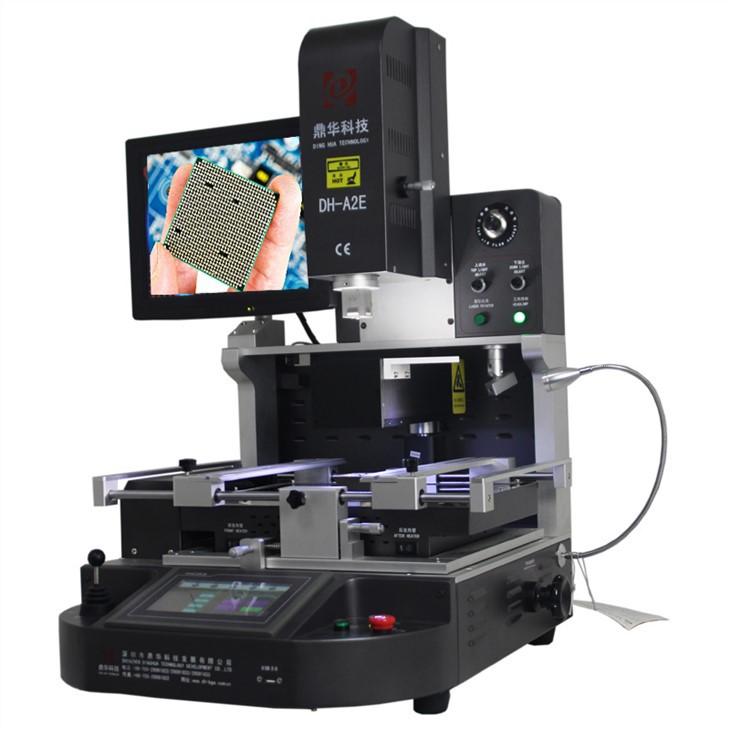

Stasiun Ulang BGA Optik Otomatis

1.Aplikasi Stasiun Ulang BGA Optik Otomatis

Motherboard komputer, ponsel pintar, laptop, papan logika MacBook, kamera digital, AC, TV, dan elektronik lainnya

peralatan dari industri medis, industri komunikasi, industri otomotif, dll.

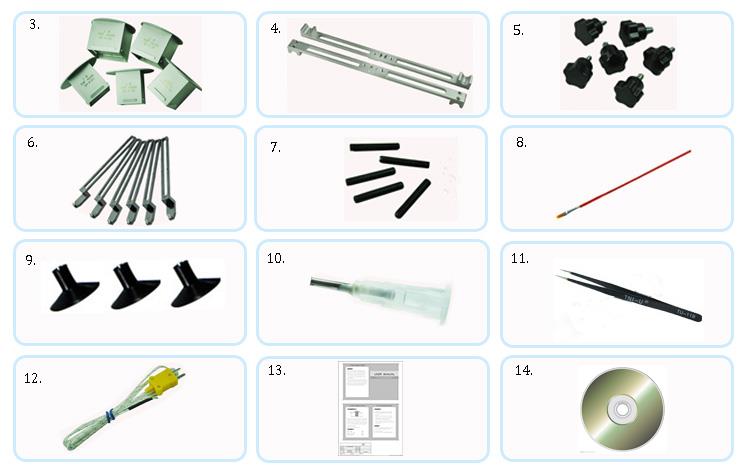

Cocok untuk berbagai jenis chip: BGA,PGA,POP,BQFP,QFN,SOT223,PLCC,TQFP,TDFN,TSOP, PBGA,CPGA,LED chip.

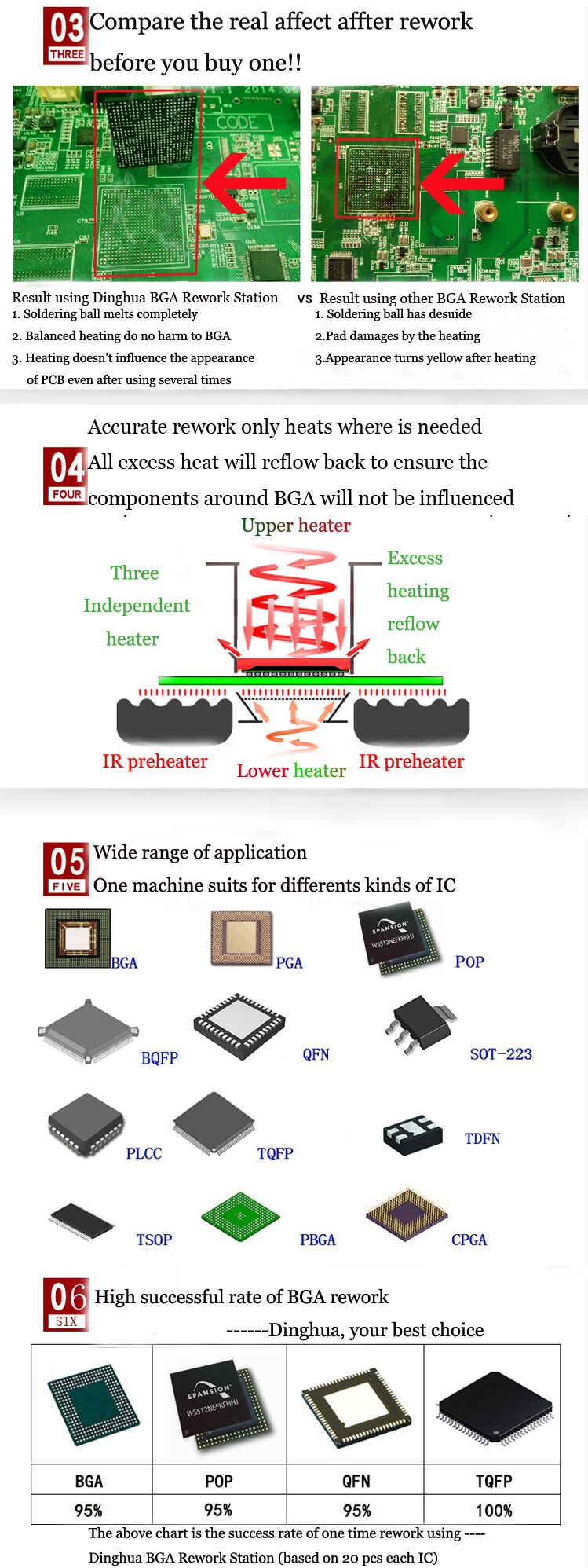

2. Fitur Produk Stasiun Pengerjaan Ulang BGA Optik Otomatis

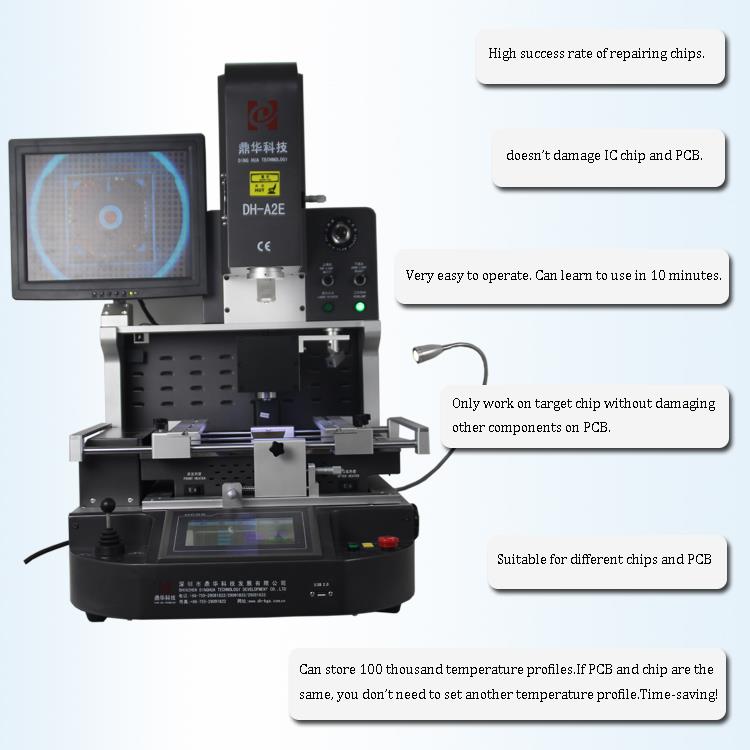

•Tingkat keberhasilan perbaikan level chip yang tinggi. Proses pematrian, pemasangan dan penyolderan otomatis.

• Penyelarasan yang tepat dari setiap sambungan penyolderan dapat dijamin dengan kamera CCD penyelarasan optik.

•Kontrol suhu yang tepat dapat dipastikan dengan 3 area pemanasan independen. Mesin dapat mengatur dan menyimpan

1 juta profil suhu.

• Build-in vakum di kepala pemasangan ambil chip BGA secara otomatis setelah pematrian selesai.

3.Spesifikasi Stasiun Ulang BGA Optik Otomatis

4.Detail Stasiun Pengerjaan Ulang BGA Optik Otomatis

Kamera CCD (sistem penyelarasan optik yang tepat); 2.HD tampilan digital; 3. Mikrometer (menyesuaikan sudut chip);

4.3 pemanas independen (udara panas & inframerah); 5. Penentuan posisi laser; 6. Antarmuka layar sentuh HD, kontrol PLC;

7.Led lampu depan; 8. Kontrol joystick.

5.Mengapa Memilih Stasiun Ulang BGA Optik Otomatis Kami?

6. Sertifikat Stasiun Pengerjaan Ulang BGA Optik Otomatis

7. Pengepakan & Pengiriman Stasiun Ulang BGA Optik Otomatis

8.FAQ

Bagaimana cara menguji chipnya?

Tes chip tingkat sistem awal

SoC didasarkan pada proses submikron yang dalam, sehingga pengujian perangkat Soc baru membutuhkan pendekatan yang benar-benar baru. Karena masing-masing komponen fungsional

memiliki persyaratan pengujiannya sendiri, insinyur desain harus membuat rencana pengujian di awal proses desain.

Rencana pengujian blok demi blok untuk perangkat SoC harus diterapkan: alat ATPG yang dikonfigurasi dengan benar untuk pengujian logika; waktu ujian singkat; kecepatan tinggi baru

model kesalahan dan beberapa memori atau tes larik kecil. Untuk lini produksi, metode diagnostik tidak hanya menemukan kesalahan, tetapi juga memisahkannya

node yang salah dari node yang bekerja. Selain itu, teknik multiplexing pengujian harus digunakan bila memungkinkan untuk menghemat waktu pengujian. Di bidang sangat

pengujian IC terintegrasi, teknik desain yang dapat diuji ATPG dan IDDQ memiliki mekanisme pemisahan kesalahan yang kuat.

Parameter aktual lainnya yang perlu direncanakan terlebih dahulu meliputi jumlah pin yang perlu dipindai dan jumlah memori di setiap ujung pin.

Pemindaian batas dapat disematkan pada SoC, tetapi tidak terbatas pada pengujian interkoneksi pada papan atau modul multi-chip.

Meskipun ukuran chip berkurang, sebuah chip masih dapat mengemas jutaan hingga 100 juta transistor, dan jumlah mode uji telah meningkat hingga belum pernah terjadi sebelumnya.

tingkat, menghasilkan siklus pengujian yang lebih lama. Masalah ini bisa diuji. Untuk memecahkan mode kompresi, rasio kompresi bisa mencapai 20 persen hingga 60 persen. Untuk skala besar saat ini

desain chip, untuk menghindari masalah kapasitas, perlu untuk menemukan perangkat lunak uji yang dapat berjalan pada sistem operasi 64-bit.

Selain itu, perangkat lunak uji dihadapkan dengan masalah pengujian baru yang disebabkan oleh proses sub-mikron yang dalam dan frekuensi yang meningkat. Di masa lalu, mode uji ATPG untuk

pengujian kesalahan pemblokiran statis tidak lagi berlaku. Menambahkan pola fungsional ke alat tradisional membuat sulit untuk menemukan kesalahan baru. Pendekatan yang lebih baik adalah dengan

mengklasifikasikan grup mode fungsional masa lalu untuk menentukan kesalahan mana yang tidak dapat dideteksi, dan kemudian membuat mode ATPG untuk menangkap jenis kesalahan yang hilang ini.

Ketika kapasitas desain meningkat dan waktu pengujian per transistor berkurang, untuk menemukan masalah terkait kecepatan dan memverifikasi waktu sirkuit, metode pengujian sinkron

harus dipekerjakan. Pengujian sinkron harus menggabungkan beberapa model kesalahan, termasuk model sementara, penundaan jalur, dan IDDQ.

Beberapa perusahaan di industri ini percaya bahwa menggabungkan kesalahan pemblokiran, fungsional, dan penundaan sementara/jalur mungkin merupakan strategi pengujian yang paling efektif. Untuk yang dalam

chip submikron dan operasi frekuensi tinggi, pengujian penundaan sementara dan jalur bahkan lebih penting.

Untuk mengatasi masalah akurasi ATE saat menyinkronkan inti pengujian dan mengurangi biaya, perlu ditemukan metode baru yang menyederhanakan antarmuka

perangkat uji (uji penundaan sementara dan jalur memerlukan jam yang akurat pada antarmuka perangkat uji), Ini memastikan bahwa sinyal cukup akurat selama pengujian.

Karena ada kemungkinan besar cacat produksi pada blok memori SoC, memori BIST harus memiliki fungsi diagnostik. Setelah masalah ditemukan,

unit alamat yang rusak dapat dipetakan ke memori redundan dari unit alamat cadangan, dan alamat kesalahan yang terdeteksi akan dibuang. Hindari membuang

seluruh chip mahal.

Menguji blok memori kecil yang disematkan menghilangkan kebutuhan akan gerbang tambahan atau logika kontrol. Misalnya, teknik pengujian konversi vektor dapat mengkonversi

mode fungsional menjadi serangkaian mode pemindaian.

Berbeda dengan metode BIST, input fungsional dari blok memori bypass tidak memerlukan logika tambahan. Karena tidak diperlukan logika pengujian tambahan, SoC

insinyur pengembangan dapat menggunakan kembali pola pengujian yang dibentuk di masa lalu.

Alat ATPG canggih tidak hanya menguji makro secara paralel tetapi juga menentukan apakah ada konflik, serta merinci makro mana yang dapat diuji secara paralel dan mana

makro tidak dapat diuji secara paralel. Selain itu, makro ini dapat diuji secara efektif meskipun jam makro sama dengan jam pemindaian (seperti memori sinkron).

Saat ini, tidak ada titik uji yang cukup pada papan dua sisi yang padat, dan setiap chip kompleks harus dilengkapi dengan sirkuit pemindaian batas. Tanpa

pemindaian batas, pencarian cacat manufaktur tingkat papan cukup sulit dan bahkan tidak dapat ditemukan. Dengan pemindaian batas, pengujian tingkat papan menjadi sangat mudah

dan independen dari sirkuit logika dalam chip. Pemindaian batas juga dapat mengonfigurasi mode ATPG ke rantai pemindaian chip pada setiap tahap produksi.